Project Description

The VHDL RTL code implements the JESD204C standard for high-speed serial communication between data converters and logic devices. It supports both 8B/10B and 64B/66B link layer modes, and can handle up to 32 Gbps lane rate and up to 8 lanes per link. It also supports subclass 0 and subclass 1 operation, with deterministic latency and SYSREF handling. It provides an AXI4 interface for configuration and status monitoring, and can be integrated with Xilinx GTP/GTX/GTH gigabit transceivers for physical layer implementation. It is compatible with Analog Devices JESD204B/C DAC converter products.

The technical specifications are:

- Link layer mode: 64B/66B

- Lane rate: up to 32 Gbps

- Number of lanes: up to 8 per link

- Subclass: 0 or 1, with deterministic latency and SYSREF handling

- Interface: AXI4 for configuration and status monitoring

- Scrambling: optional, for EMI reduction

- Character replacement: optional, for EMI reduction

- Physical layer: compatible with Xilinx GTP/GTX/GTH gigabit transceivers

- Compatibility: Xilinx JESD204C IP Core

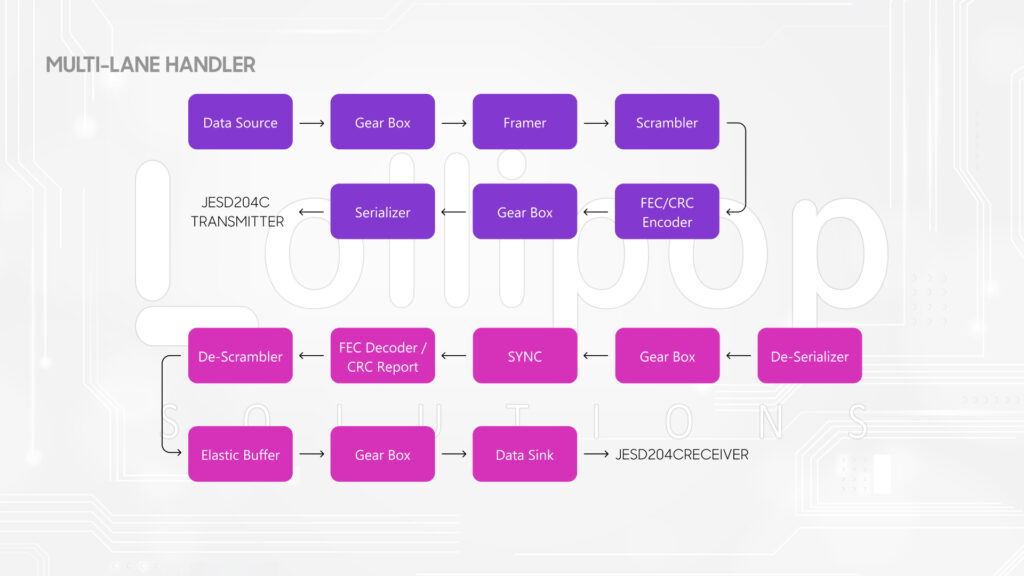

The coding block in my VHDL RTL code consists of the following modules:

• Transport layer: maps the conversion between samples and framed, unscrambled octets

• Scramble layer: scrambles/descrambles the octets, spreading the spectral peaks to reduce EMI

• Data-link layer: handles link synchronization, setup, and maintenance, and encodes/decodes the optionally scrambled octets to/from 10-bit characters

• Physical layer: responsible for transmission and reception of characters at the bit rate